# IEC 61000-4-16 の概要 — 追補 2: AC 電圧試験における結合回路による終端の影響

株式会社 e・オータマ 佐藤智典

2025 年 12 月 8 日

## 目次

|       |                                    |    |

|-------|------------------------------------|----|

| 1     | 概要                                 | 1  |

| 2     | デジタル I/O ポート、デジタル通信ポート             | 2  |

| 2.1   | 非絶縁 NPN オープン・コレクタ出力 → 抵抗プルアップ、電圧入力 | 2  |

| 2.1.1 | 通常の動作                              | 2  |

| 2.1.2 | ポートの終端の影響                          | 2  |

| 2.1.3 | 終端の影響の軽減/回避                        | 4  |

| 2.2   | 非絶縁 NPN オープン・コレクタ出力 → リレー負荷        | 5  |

| 2.3   | 非絶縁 PNP オープン・コレクタ出力 → フォトカプラ絶縁入力   | 5  |

| 2.3.1 | 通常の動作                              | 5  |

| 2.3.2 | ポートの終端の影響                          | 6  |

| 2.3.3 | 終端の影響の軽減/回避                        | 7  |

| 2.4   | フォトカプラ絶縁入力 ← 非絶縁 NPN オープン・コレクタ出力   | 7  |

| 2.4.1 | 通常の動作                              | 8  |

| 2.4.2 | ポートの終端の影響                          | 8  |

| 2.4.3 | 終端の影響の軽減/回避                        | 9  |

| 3     | アナログ I/O ポート                       | 9  |

| 3.1   | アナログ信号 定電流ソース → 抵抗負荷、絶縁増幅器入力       | 9  |

| 3.1.1 | 通常の動作                              | 9  |

| 3.1.2 | ポートの終端の影響                          | 10 |

| 4     | まとめ                                | 10 |

| 5     | 参考資料                               | 10 |

## 1 概要

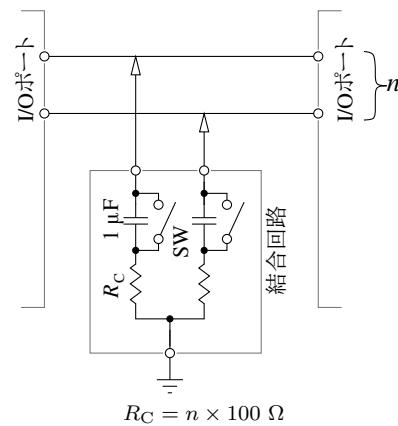

IEC 61000-4-16<sup>[1][2]</sup> の試験に際して、妨害の注入の対象となる非シールド線の接続が意図されたポートはそのポートに妨害を注入する時以外は図 1 のように結合回路を介して接地することで終端<sup>[1]</sup>することになるだろう。

この終端は抵抗と直列に  $1 \mu\text{F}$  のコンデンサが接続されて直流分を遮断することから、DC 電圧試験に際しての終端<sup>[2.1]</sup> と比較してポートの動作には影

<sup>[1]</sup> そのポートの AE (対向器) 側は何らかの手段によって他からアイソレートされ、この結合回路は EUT から見たコモン・モード・インピーダンスを  $100 \Omega$  とすることから、規格ではその用語は用いられていないが本稿では “終端” と呼ぶ。

響を与えにくくなっている。だが、それでもこれがポートの動作に無視できない影響を与え、試験の適切な実施を妨げることがある。

図 1: 妨害が印加されていないポートの終端の例

本稿では IEC 61000-4-16 のこの AC 電圧試験における “AC 終端” によって生じることがある問題の例について、またその一部については可能かも知れない対処方法<sup>[2][3]</sup>について述べる。

そのポートに妨害を注入する際には例えば AC  $\pm 10 \text{ V}$  や AC  $\pm 100 \text{ V}$  の妨害電圧が  $50 \Omega$  の抵抗を介して結合回路に注入され、そのポートの各端子に高い電圧や電流を生じさせることが予期される<sup>[4]</sup>が、これは本稿では扱わない。

<sup>[2]</sup> ここで示す対処方法は回路定数や回路そのものの変更を伴い、それが試験対象のシステムの動作や試験に悪影響を与えるいかどうかは別途検討が必要となるであろう。

<sup>[3]</sup> 回路定数や回路そのものの変更を行なった EUT を試験所で試験する場合、その変更の情報はテスト・プランに含めるか、あるいは試験後に速やかにテスト・プランの追補として提出することが望ましいだろう。

<sup>[4]</sup> 本稿で示した回路のいくつかはそのような妨害に耐えられないことが予期される。長距離での接続には耐性の高い回路の使用を、及び/もしくはシールドの適切な適用を考慮することを推奨する。

また、DC 電圧試験に際しては結合回路の SW を閉じて  $1\ \mu\text{F}$  のコンデンサを短絡するが、これは既に別の記事<sup>[2,1]</sup>で扱っており、本稿では扱わない。

## 2 デジタル I/O ポート、デジタル通信ポート

### 2.1 非絶縁 NPN オープン・コレクタ出力 → 抵抗プルアップ、電圧入力

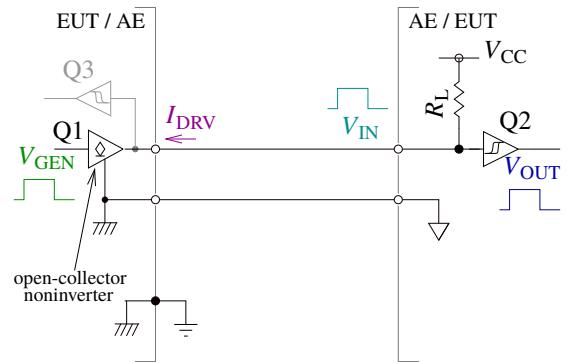

ここでは、図 3<sup>†5</sup>に示すような、オープン・コレクタの出力を抵抗 ( $R_L$ ) でプルアップして論理信号として受け取る単純な非絶縁インターフェースについて考える。

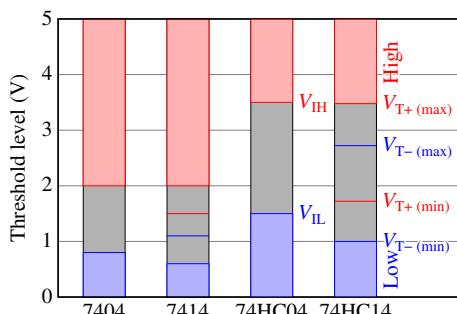

受信レベルのロー/ハイの判別の閾値  $V_T$  はレシーバに依存し、レシーバとして標準ロジックを用いるとしてもファミリや電源電圧による相違が、またファミリ内でも若干の相違がある。さらに、実際の閾値は図 2 でグレー・ゾーンとして示した広い範囲内のどこかにあり、シユミット・トリガの場合は電圧の立ち上がりと立ち下がりとで異なる閾値を持つが、本稿では特に示した場合を除きここでの分析の上で悲観的なものとなるであろう図 2 で例示した 74HC14 の立ち上がりの閾値の最大値  $V_{T+}(\text{max})$  と、また 74HC04 のハイ・レベルの閾値と等しい単一の閾値を持つものと仮定する。

図 2: ロジック入力の閾値の例 ( $V_{CC} = 5\ \text{V}$ )

#### 2.1.1 通常の動作

結合回路を接続していない通常の動作状態では、 $V_{GEN}$  がローの時は受信端の電圧  $V_{IN}$  はドライバ

<sup>†5</sup> ここでは実際には存在するかも知れないフィルタや保護回路は示していない。以下も同様。

図 3: 非絶縁 NPN オープン・コレクタ出力 → 抵抗プルアップ、電圧入力

$Q_1$  によって 0 V 近くまで引き下げられてレシーバ  $Q_2$  の出力  $V_{OUT}$  はローとなる。

また、 $V_{GEN}$  がハイの時はドライバ  $Q_1$  のオープン・コレクタ出力は遮断状態となり、受信端の電圧  $V_{IN}$  はプルアップ抵抗  $R_L$  によって受信側の  $V_{CC}$  近くまで引き上げられてレシーバ  $Q_2$  の出力  $V_{OUT}$  はハイとなる。

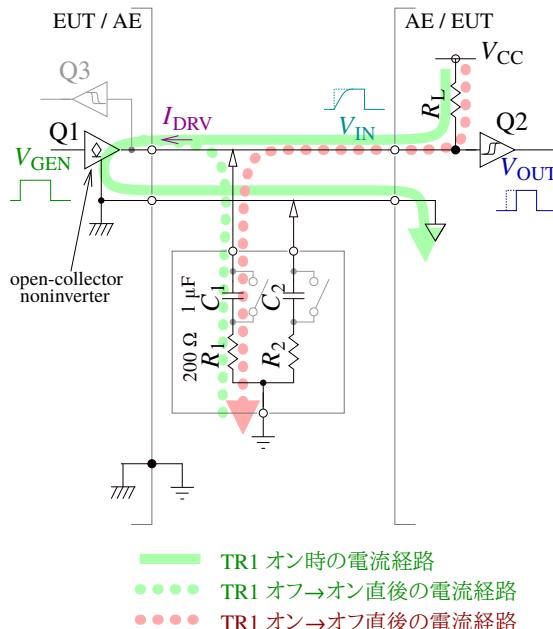

#### 2.1.2 ポートの終端の影響

このラインを結合回路で AC 終端した時、図 4 に示すように結合回路の  $C_1$  と  $R_1$  ( $1\ \mu\text{F}$  と  $200\ \Omega$ ) を直列としたものが受信端と並列に接続されたような形<sup>†6</sup>となり、これが信号の立ち上がり/立ち下がりの挙動に影響を与えることが予期される。

$V_{GEN}$  がハイとなってドライバ  $Q_1$  のオープン・コレクタ出力が遮断状態となるとプルアップ抵抗  $R_L$  が受信端の電圧  $V_{IN}$  を引き上げようとする。だが、そこには  $C_1$  と  $R_1$  が接続されていることから、 $V_{IN}$  を  $V_{CC}$  の  $R_L$  と  $R_1$  での分圧、 $V_{CC} \cdot R_1 / (R_L + R_1)$  よりも上に引き上げるためには  $C_1$  が充電されることが必要となる。コンデンサ  $C_1$  はプルアップ抵抗  $R_L$  と結合回路の抵抗  $R_1$  を通して充電され、その時定数は  $\tau = (R_L + R_1)C_1 = (R_L + 200\ \Omega) \times 1\ \mu\text{F}$  となる。受信端の電圧  $V_{IN}$  は  $C_1$  の充電に伴って上昇し、 $V_{IN}$  が閾値  $V_T$  を超えるとレシーバ  $Q_2$  の出力  $V_{OUT}$  はハイとなる。

<sup>†6</sup> 結合回路はグランドとのあいだに接続され、それに対して受信側 (AE 側) はフローティングであるため、受信端と並列に接続されるという表現はあまり適切ではないかも知れない。だが、ここで仮定した構成 (図 4) では低周波においては結合回路の RC は結局は受信端と並列に接続されるのと同様となるため、ここではそのように表現している。他も同様。

図 4: 非絶縁 NPN オープン・コレクタ出力 → 抵抗プルアップ、電圧入力 — 結合回路による AC 終端

このため、 $V_{OUT}$  の立ち上がりはプルアップ抵抗  $R_L$  (また閾値  $V_T$ ) に依存して相当の遅れを生じることが予期される。

一方、 $V_{GEN}$  がローとなるとドライバ Q1 の出力のトランジスタは導通し、コンデンサ  $C_1$  に蓄えられていた電荷はドライバ Q1 と  $R_1$  とを通して放電される。だが、 $V_{IN}$  はドライバ Q1 によって  $C_1$  の放電を待たずに素早く引き下げられ、それに伴ってレシーバ Q2 の出力  $V_{OUT}$  はローとなる。

従って、その立ち上がりと異なり、 $V_{OUT}$  の立ち下がりについては顕著な遅れは予期されない。

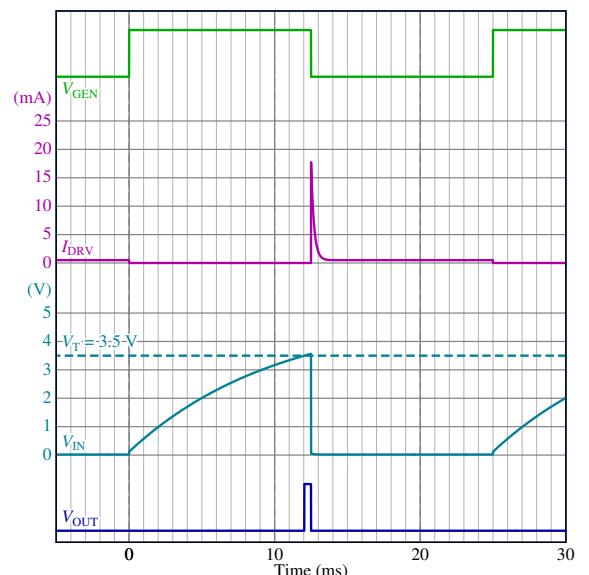

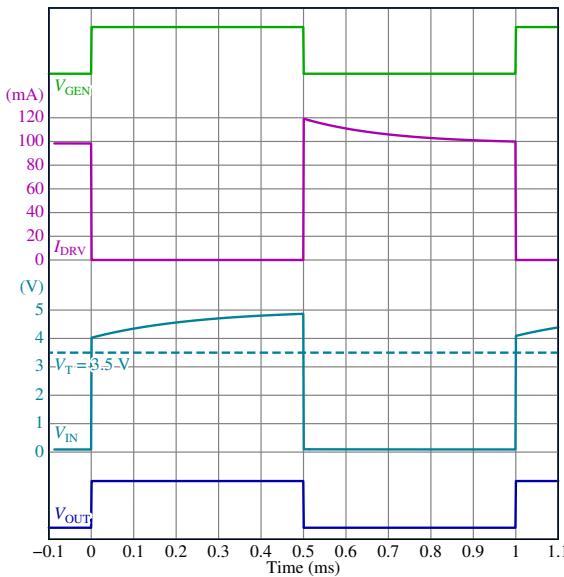

例えば 図 5 に電源電圧  $V_{CC} = 5$  V、閾値  $V_T = 3.5$  V、プルアップ抵抗  $R_L = 10$  kΩ と仮定して推定した各部の波形を示す。

この条件では充電時定数  $\tau = (10 \text{ k}\Omega + 200 \Omega) \times 1 \mu\text{F} = 10.2 \text{ ms}$  となり、 $V_{IN}$  は約 10 ms で  $0.632 V_{CC} = 3.16 \text{ V}$ <sup>†7</sup> を超え、それよりも少し長い時間でここで仮定した閾値  $V_T (= 3.5 \text{ V})$  を超える計算となる。

図 5 を見ると、 $V_{GEN}$  がハイとなると  $V_{IN}$  は 0 V から緩やかに上昇して 10 ms 強で  $V_T$  を超え、そのタイミングで  $V_{OUT}$  が立ち上がっていることが、

従って  $V_{OUT}$  の立ち上がりは  $V_{GEN}$  の立ち上がりから 10 ms 強遅れていることがわかるだろう。

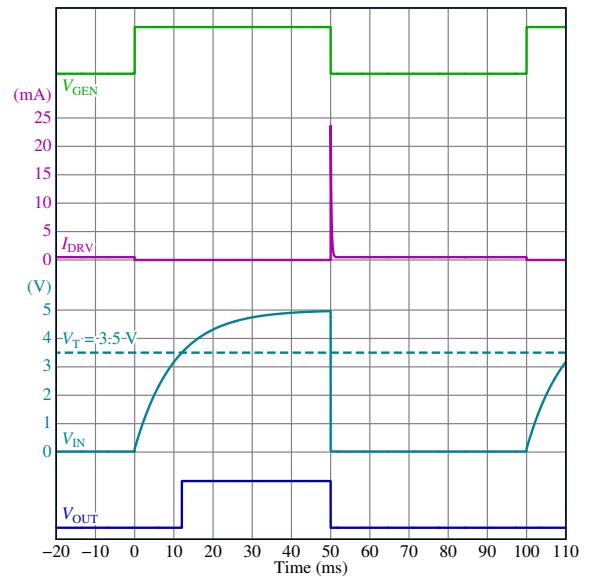

ここで仮定した条件では、 $f_{GEN} = 40 \text{ Hz}$  ( $V_{GEN}$  の正のパルス幅が 12.5 ms) 程度となると図 6 に示すように  $V_{OUT}$  の正のパルス幅は著しく小さくなり、 $V_{GEN}$  の正のパルス幅がこの程度以下となると

<sup>†7</sup> RC 回路の充電電圧のカーブは、時定数を  $\tau = RC$ 、入力電圧を  $V_0$ 、コンデンサの両端の電圧を  $V_C$  として、 $V_C = V_0 (1 - e^{-t/\tau})$  で、時間  $t = \tau$  における電圧は  $V_C = V_0 (1 - e^{-1}) = 0.632 V_0$  となる。

図 7: 非絶縁 NPN オープン・コレクタ出力 → 抵抗プルアップ、電圧入力 (図 4,  $R_L = 1 \text{ k}\Omega$ ,  $f_{\text{GEN}} = 40 \text{ Hz}$ )

図 8: 非絶縁 NPN オープン・コレクタ出力 → 抵抗プルアップ、電圧入力 (図 4,  $R_L = 1 \text{ k}\Omega$ ,  $f_{\text{GEN}} = 400 \text{ Hz}$ )

$V_{\text{OUT}}$  には細いパルスさえ現われないようになることが予期される。<sup>†8</sup>

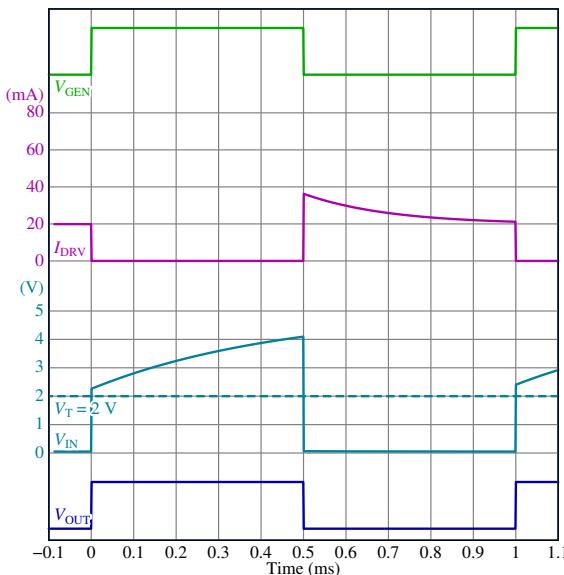

$R_L = 1 \text{ k}\Omega$  の場合は充電時定数  $\tau = (1 \text{ k}\Omega + 200 \Omega) \times 1 \mu\text{F} = 1.2 \text{ ms}$  となり、この条件では  $f_{\text{GEN}} = 40 \text{ Hz}$  での波形は図 7 のように改善されることが期待される。だが、この条件でも  $f_{\text{GEN}} =$

<sup>†8</sup> 勿論、この推定はかなり悲観的なものである。例えば実際の閾値がこれよりも低ければこの影響による  $V_{\text{OUT}}$  の立ち上がりの遅延はそれに応じて小さくなるであろう。

400 Hz ( $V_{\text{GEN}}$  の正のパルス幅 1.25 ms) 程度で図 8 のようになるかも知れない。

ここで図 8 を見ると  $V_{\text{IN}}$  の波形が約 1 V まで素早く立ち上がっているのが見える。これは  $V_{\text{CC}}$  の  $R_L$  と  $R_1$  での分圧、 $V_{\text{CC}} \cdot R_1 / (R_L + R_1) = 5 \text{ V} \cdot 200 \Omega / (1 \text{ k}\Omega + 200 \Omega) \simeq 0.83 \text{ V}$  の影響であり、これはそれほど目立たないが図 7 などにも現れている。

上で述べたように、図 4 のようなポートの結合回路による AC 終端に伴って信号の立ち上がりが有意に遅くなる可能性が予期されるが、これは例えば次のような理由からシステムの動作上の、あるいは試験の実施上の問題を引き起こすかも知れない：

- 通信やその他の早いパルス<sup>†9</sup>の正常な伝達が妨げられる；

- 正のパルスとして送られた信号が失われる；<sup>†10</sup>

- パルスのデューティーとして伝送されるアナログ値に無視できない誤差を生じる；

- 機器自身に出力を監視する機能 (図 4 で Q3 として示したような) が組み込まれている場合、出力している箇の信号と出力された信号が一致しないとして障害が発生したものと判断される；

- 複数の接続がある場合のタイミングのずれや受信側の機器の動作の遅れが異常の判定や障害を引き起こす；

- レシーバの入力電圧が閾値を緩やかに横切るようになることから、閾値付近でレシーバの出力が不安定となる；

- イミュニティ評価の目的で準備された監視手段で、出力している箇の信号と受信された信号とが一致しないことから動作が正常でないと判断される。

### 2.1.3 終端の影響の軽減/回避

ドライバ (図 4 の TR1) がそれを駆動できる場合、プルアップ抵抗  $R_L$  を小さくして  $V_T < V_{\text{CC}} \cdot$

<sup>†9</sup> 例えばエンコーダの出力やパルス周波数に変換されたアナログ値のような。

<sup>†10</sup> このタイプのインターフェースは負論理で用いられることが多いと思われ、その場合はこれはそれほど問題となりそうにない。

図 9: 非絶縁 NPN オープン・コレクタ出力 → 抵抗プルアップ、電圧入力 (図 4,  $R_L = 50 \Omega$ ,  $f_{GEN} = 1 \text{ kHz}$ )

図 10: 非絶縁 NPN オープン・コレクタ出力 → 抵抗プルアップ、電圧入力 (図 4,  $R_L = 250 \Omega$ ,  $f_{GEN} = 1 \text{ kHz}$ ,  $V_T = 2 \text{ V}$ )

$R_1/(R_L + R_1)$  となるようにすることができれば、この種の問題を回避、あるいは少なくとも相当の程度まで緩和できる可能性がある。

例えば  $R_L = 50 \Omega$  とすれば  $5 \text{ V} \cdot 200 \Omega/(50 \Omega + 200 \Omega) = 4 \text{ V}$  となり、図 9 に図示するように  $V_{IN}$  は  $C_1$  の充放電を待たずにここで仮定した閾値  $V_T$  ( $= 3.5 \text{ V}$ ) を横切るようになる。

また、レシーバの閾値  $V_T$  が低い、あるいは低くできる場合、 $R_L$  をそこまで小さくしなくても同様

の効果を得られるであろう。例えば図 2 で例示した 7414 の場合は立ち上がりの閾値が  $2 \text{ V}$  以下と想定され、 $R_L = 250 \Omega$  でも  $5 \text{ V} \cdot 200 \Omega/(250 \Omega + 200 \Omega) = 2.2 \text{ V}$  となってその閾値を超えるため、図 10 に図示するように同様の効果が予期される。

このような条件を満たすようにできれば、ドライバの負荷が重くなることによる若干の速度の低下などはあるかも知れないものの、結合回路を接続していない時に近い応答速度が期待できそうだ。

$R_L$  をここまで小さくできない場合も、上で  $R_L$  を  $10 \text{ k}\Omega$  から  $1 \text{ k}\Omega$  に変更した場合として示したように、 $R_L$  を可能な範囲で小さくして充電時定数  $\tau = (R_L + R_1)C_1$  を小さくすれば、その分は応答を改善することができる。

場合によっては、応答を改善するのではなく、応答の遅れを許容するようにシステムの動作を変更することでの対処も可能かも知れない。

## 2.2 非絶縁 NPN オープン・コレクタ出力 → リレー負荷

負荷がリレーの場合も、負荷が抵抗の場合 (§2.1) と同様に結合回路による AC 終端に伴う駆動電流の応答の遅れを生じる可能性がある。

これはリレー自身の機械的な応答時間 (例えば ms から  $10 \text{ ms}$  のオーダー) と比較して無視できるものとなるとは限らないものの、それが実際上の問題となることは相当稀と思われる所以、これには踏み込まない。

## 2.3 非絶縁 PNP オープン・コレクタ出力 → フォトカプラ絶縁入力

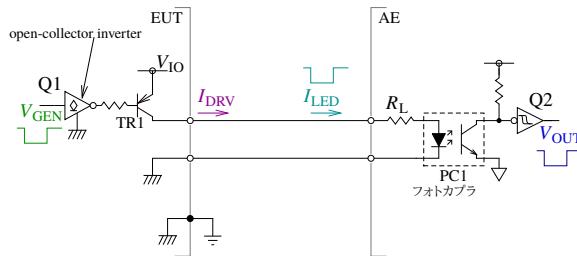

ここでは、図 11 のように EUT 側から PNP オープン・コレクタでソースされる電流を AE 側のフォトカプラで受ける場合について考える。

### 2.3.1 通常の動作

結合回路を接続していない通常の動作状態では、 $V_{GEN}$  がローの時はインバータ  $Q_1$  のオープン・コレクタ出力は遮断状態となって  $TR1$  も遮断され、フォトカプラ  $PC1$  の LED には電流は流れず、フォトカプラの出力にも電流は流れず、インバータ  $Q2$

図 11: 非絶縁 PNP オープン・コレクタ出力 → フォトカプラ絶縁入力

の入力はプルアップによってハイ・レベルとなり、その出力  $V_{OUT}$  はローとなる。

$V_{GEN}$  がハイとなるとインバータ  $Q_1$  の出力のトランジスタが導通して  $TR_1$  も導通し、フォトカプラ  $PC_1$  の LED にインバータ  $Q_2$  の入力をロー・レベルとする閾値  $I_T$  を超える電流が流れ、インバータ  $Q_2$  の入力は引き下げられてロー・レベルとなり、その出力  $V_{OUT}$  はハイとなる。

### 2.3.2 ポートの終端の影響

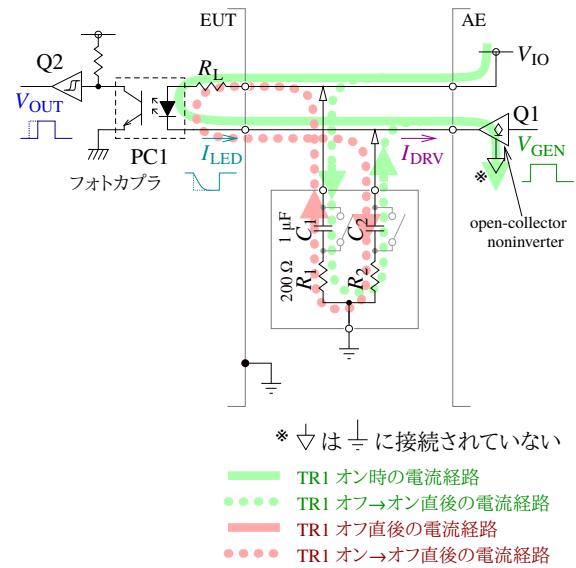

このラインを結合回路で AC 終端した時、図 12 に示すように結合回路の  $C_1$  と  $R_1$  ( $1 \mu F$  と  $200 \Omega$ ) を直列としたものが受信端と並列に接続されたような形となり、これが信号の立ち上がり/立ち下がりの挙動に影響を与えることが予期される。

図 12: 非絶縁 PNP オープン・コレクタ出力 → フォトカプラ絶縁入力 — 結合回路による AC 終端

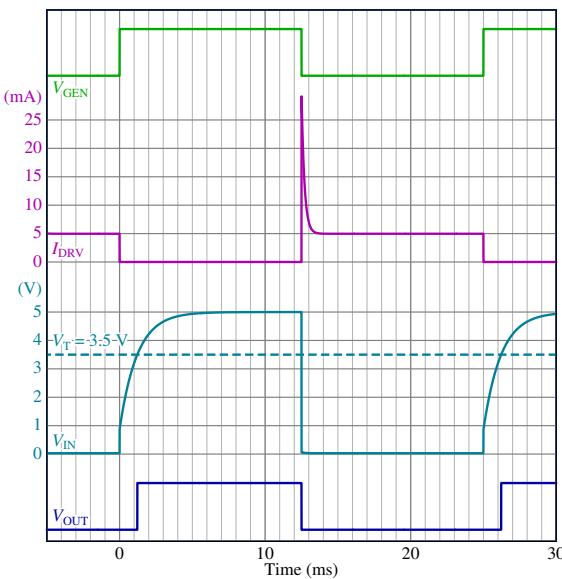

$V_{GEN}$  がハイとなって  $TR_1$  が導通すると、フォトカプラ  $PC_1$  の LED に通電して  $V_{OUT}$  がハイとなるとともに、 $C_1$  は  $V_{IO}$  まで時定数  $\tau = R_1 \cdot C_1 = 200 \Omega \times 1 \mu F = 0.2 \text{ ms}$  で充電される。

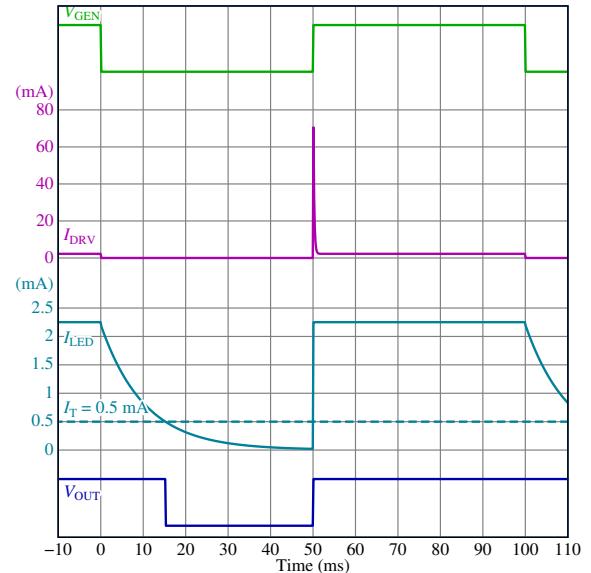

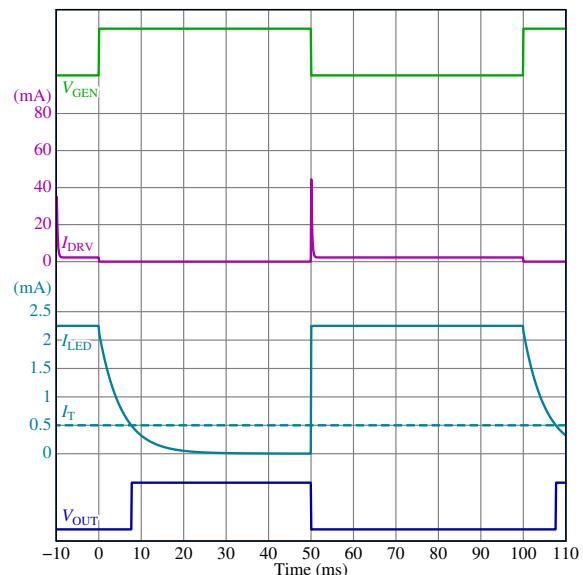

図 13: 非絶縁 PNP オープン・コレクタ出力 → フォトカプラ絶縁入力 (図 12,  $V_{IO} = 24 \text{ V}$ ,  $R_L = 10 \text{ k}\Omega$ , 閾値  $I_T = 0.5 \text{ mA}$  として  $I_{LED} < I_T$  で  $V_{OUT}$  がハイとなると仮定)

$V_{GEN}$  がローとなって  $TR_1$  が遮断した時、少しのあいだは  $C_1$  に残された電荷がフォトカプラ  $PC_1$  の LED を通して放電され、その電流が閾値  $I_T$  よりも大きいあいだは  $V_{OUT}$  はハイのままとなる。この電流は  $C_1$  の放電に伴って減衰し、それが閾値  $I_T$  を超えて低下すると  $V_{OUT}$  はローとなる。

このため、このケースではパルスの立ち下がりが電流の減衰のカーブや閾値  $I_T$  に依存した遅れを生じることになる。

この電流の減衰のカーブは、LED の非線形性の影響も受けるものの、LED と直列に接続された電流制限抵抗を  $R_L$  として概ね時定数  $\tau = (R_L + R_1)C_1$  の減衰カーブとなり、 $R_L$  の影響を強く受ける。

立ち下がりの遅れが比較的大きくなるような条件、 $V_{IO} = 24 \text{ V}$ ,  $R_L = 10 \text{ k}\Omega$ , 閾値  $I_T = 0.5 \text{ mA}$  として推定した波形を図 13 に示すが、この条件では  $V_{OUT}$  の立ち下がりは  $V_{GEN}$  の立ち上がりから 15 ms 程度遅れると推定されている。

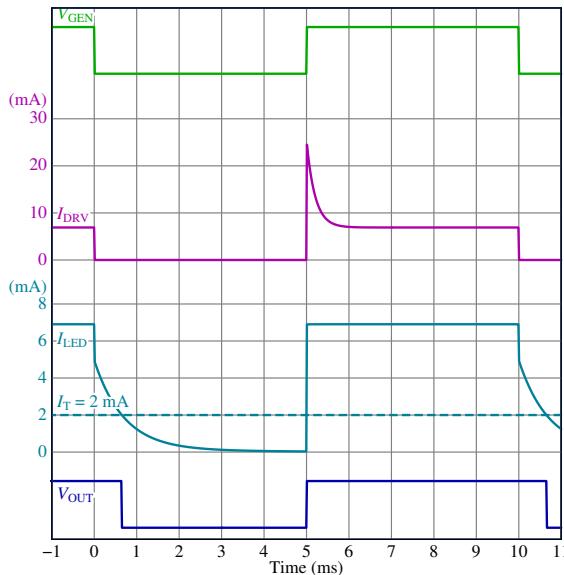

また、 $V_{IO} = 5 \text{ V}$ ,  $R_L = 500 \Omega$ , 閾値  $I_T = 2 \text{ mA}$  として推定した波形を図 14 に示すが、この条件では立ち下がりの遅れは 1 ms 未満と推定されている。

上で述べたような応答の遅れは、例えば「正のパルス」とあるところが「負のパルス」となることを除き §2.1.2 で述べたものと同様の理由から、システ

図 14: 非絶縁 PNP オープン・コレクタ出力 → フォトカプラ絶縁入力 (図 12,  $V_{IO} = 5\text{ V}$ ,  $R_L = 500\Omega$ , 閾値  $I_T = 2\text{ mA}$  として  $I_{LED} < I_T$  で  $V_{OUT}$  がハイとなると仮定)

ムの動作上の、あるいは試験の実施上の問題を引き起こすかも知れない。

### 2.3.3 終端の影響の軽減/回避

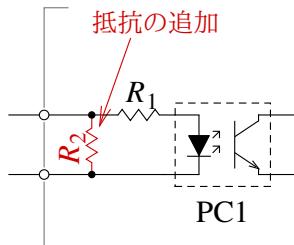

この問題は例えば図 17 のように受信端と並列<sup>†11</sup>に抵抗を接続することで軽減できる可能性がある。

例えば他は図 13 と同じ条件で、受信端と並列に  $500\Omega$  の抵抗を接続した場合の波形を推定したものを図 15 に示すが、 $I_{LED}$  の立ち下がりがかなり早く、 $V_{OUT}$  の立ち下がりの遅れがかなり小さくなっているのがわかるだろう。

また、抵抗値が  $I_T R_1 R_L / (V_{IO} - I_T R_L)$  よりも小さい抵抗を受信端と並列に接続すれば  $C_1$  の放電を待たずに  $I_{LED} < I_T$  となるように、従って応答の有意な遅れを生じないようにできるであろう。

例えば図 13 と同じ条件では  $50\Omega$  の抵抗を受信端と並列に接続すれば TR1 が遮断された直後の受信端の電圧は  $V_{IO} \cdot 50\Omega / (200\Omega + 50\Omega) = 4.8\text{ V}$  に、従ってフォトカプラの LED に流れる電流は LED の順電圧を無視しても  $4.8\text{ V} / R_L = 0.48\text{ mA}$  となり、図 16 に図示するように、単純には TR1 が遮断された直後に  $I_{LED} < I_T$  となる計算となる。

<sup>†11</sup> 図 12 の回路から明らかなように、低周波においては、この追加の抵抗は物理的には送信端に接続しても、あるいはライン上のどの位置に接続しても同様である。他も同様。

図 15: 非絶縁 PNP オープン・コレクタ出力 → フォトカプラ絶縁入力 (他は図 13 と同じ条件で、受信端と並列に  $500\Omega$  の抵抗を接続した場合を仮定)

図 16: 非絶縁 PNP オープン・コレクタ出力 → フォトカプラ絶縁入力 (他は図 13 と同じ条件で、受信端と並列に  $50\Omega$  の抵抗を接続した場合を仮定)

### 2.4 フォトカプラ絶縁入力 ← 非絶縁 NPN オープン・コレクタ出力

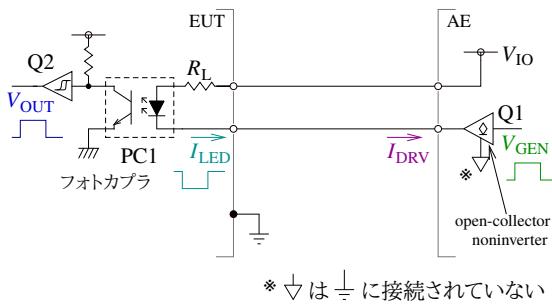

ここでは §2.3 と似ているが EUT と AE が逆の、すなわち図 18 のように AE 側からの単純な非絶縁オープン・コレクタの出力を EUT 側のフォトカプラで受ける場合について考える。

図 17: 非絶縁 PNP オープン・コレクタ出力 → フォトカプラ絶縁入力 — 抵抗の追加 (§2.3.3)

図 18: フォトカプラ絶縁入力 (EUT 側) ← 非絶縁 NPN オープン・コレクタ出力 (AE 側)

#### 2.4.1 通常の動作

結合回路を接続していない通常の動作状態では、 $V_{GEN}$  がハイの時は Q1 のオープン・コレクタ出力は遮断状態となってフォトカプラの LED には電流は流れず、フォトカプラの出力にも電流は流れず、レシーバ Q2 の入力はプルアップによってハイ・レベルとなり、レシーバ Q2 の出力  $V_{OUT}$  はハイとなる。

$V_{GEN}$  がローとなると Q1 の出力のトランジスタが導通してフォトカプラの LED にレシーバ Q2 の入力をロー・レベルとする閾値  $I_T$  を超える電流が流れ、レシーバ Q2 の入力は引き下げられてロー・レベルとなり、レシーバ Q2 の出力  $V_{OUT}$  はローとなる。

#### 2.4.2 ポートの終端の影響

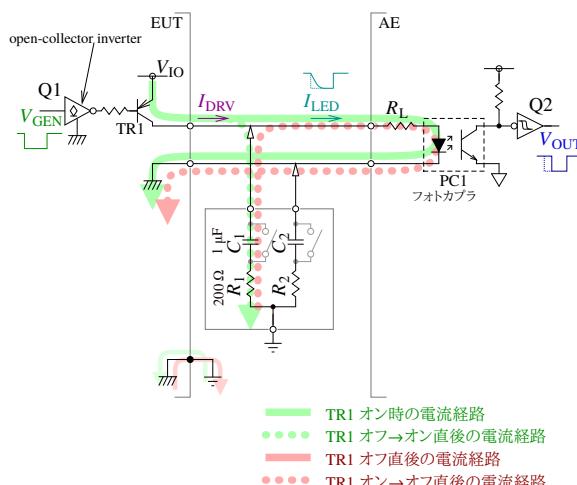

このケースでは §2.3 と異なりグランドに電流が抜けることがないため、図 19 のように結合回路の  $C_1$ 、 $R_1$ 、 $C_2$ 、及び  $R_2$  ( $1 \mu\text{F}/2 = 0.5 \mu\text{F}$  と  $200 \Omega \times 2 = 400 \Omega$ ) を直列としたものが受信端と並列に接続されたような形となる。

$V_{GEN}$  がローとなって Q1 の出力のトランジスタが導通するとフォトカプラ PC1 の LED に通電し

図 19: フォトカプラ絶縁入力 (EUT 側) ← 非絶縁 NPN オープン・コレクタ出力 (AE 側) — 結合回路による AC 終端

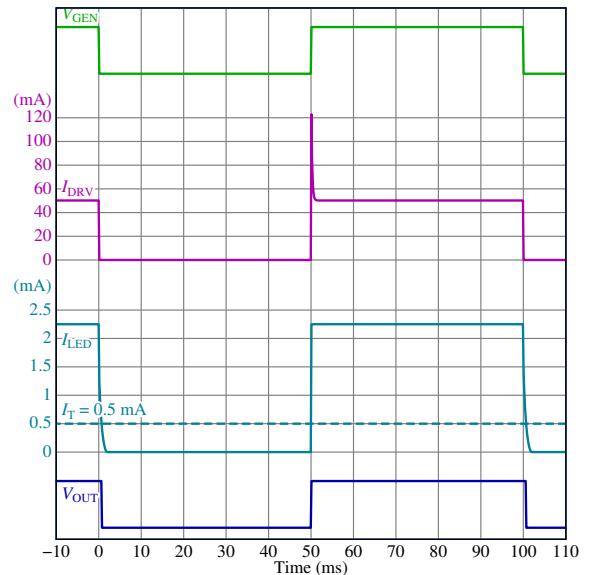

図 20: フォトカプラ絶縁入力 (EUT 側) ← 非絶縁 NPN オープン・コレクタ出力 (AE 側) (図 19,  $V_{IO} = 24 \text{ V}$ ,  $R_L = 10 \text{ k}\Omega$ , 閾値  $I_T = 0.5 \text{ mA}$  として  $I_{LED} < I_T$  で  $V_{OUT}$  がローとなると仮定)

て  $V_{OUT}$  がローとなると共に、 $C_1$  は  $V_{IO}$  まで時定数  $\tau = 400 \Omega \times 0.5 \mu\text{F} = 0.2 \text{ ms}$  で充電される。

$V_{GEN}$  がハイとなって Q1 のオープン・コレクタ出力が遮断状態となると少しのあいだは  $C_1$  に残された電荷がフォトカプラ PC1 の LED を通して放電され、その電流が閾値  $I_T$  よりも大きいあいだは  $V_{OUT}$  はローのままとなる。この電流は  $C_1$  の放電

図 21: フォトカプラ絶縁入力 (EUT 側)  $\leftarrow$  非絶縁 NPN オープン・コレクタ出力 (AE 側) (図 19,  $V_{IO} = 5$  V,  $R_L = 500 \Omega$ , 閾値  $I_T = 0.5$  mA として  $I_{LED} < I_T$  で  $V_{OUT}$  がハイとなると仮定)

に伴って減衰し、それが閾値  $I_T$  を超えて低下すると  $V_{OUT}$  はハイとなる。

このため、このケースではパルスの立ち上がりが電流の減衰のカーブや閾値  $I_T$  に依存した遅れを生じることになる。

例えば図 20に図 13と同様の条件で推定した波形を示すが、図 13と比較して  $I_{LED}$  の減衰が早くなっており、 $V_{OUT}$  の立ち下がり (図 13では立ち上がり) の遅れが半分程度となっていることがわかるだろう。

上で述べたような応答の遅れは、例えば「正のパルス」とあるところが「負のパルス」となることを除き §2.1.2で述べたものと同様の理由から、システムの動作上の、あるいは試験の実施上の問題を引き起こすかも知れない。

#### 2.4.3 終端の影響の軽減/回避

§2.4 の場合と同様、この問題は受信端と並列に抵抗を接続することで軽減/回避できる可能性がある。

このケースでは、抵抗値が  $I_T \cdot 2R_1 R_L / (V_{IO} - I_T R_L)$  よりも小さい抵抗を受信端と並列に接続すれば  $C_1$  の放電を待たずに  $I_{LED} < I_T$  となるよう、従って応答の有意な遅れを生じないようにできるであろう。

例えば図 20と同じ条件では  $100 \Omega$  の抵抗を受信端と並列に接続すれば TR1 が遮断された直後の受信端の電圧は  $V_{IO} \cdot 100 \Omega / (200 \Omega \times 2 + 100 \Omega) = 4.8$  V に、従ってフォトカプラの LED に流れる電流は  $I_{LED} \lesssim 4.8 \text{ V} / R_L = 0.48$  mA となり、TR1 が遮断された直後に  $I_{LED} < I_T$  となる計算となる。

### 3 アナログ I/O ポート

アナログ信号をシールドせずに長い距離引くことは稀と思われ、ここでは 4-20 mA についてのみ検討する。

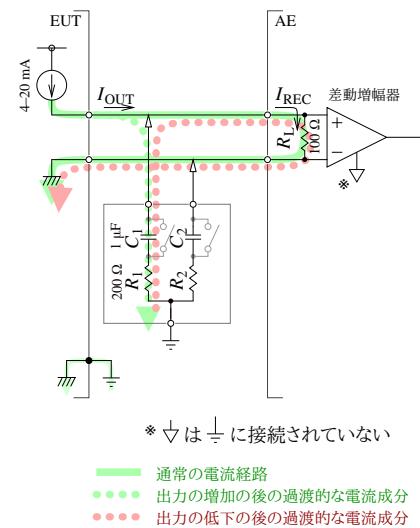

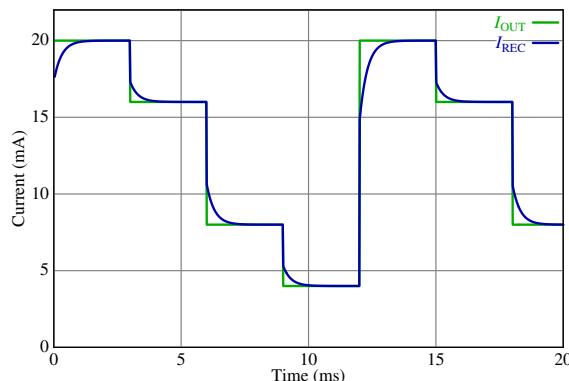

#### 3.1 アナログ信号 定電流ソース $\rightarrow$ 抵抗負荷、絶縁増幅器入力

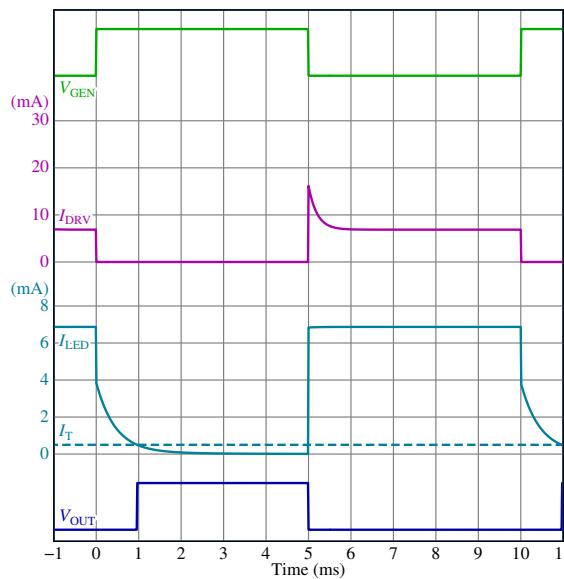

ここでは図 22 のような EUT 側から定電流でソースされるアナログ信号電流  $I_{DRV}$  を AE 側で検出抵抗  $R_L$  で受けている場合について考える。

図 22: アナログ信号 定電流ソース  $\rightarrow$  抵抗負荷、絶縁増幅器入力

ソース側 (EUT 側) は絶縁されておらず、受信側 (AE 側) は絶縁増幅器かその他の何らかの手段でグランドや他の使用されるポートから絶縁された状態とされるものと想定している。

##### 3.1.1 通常の動作

出力側からソースされた電流  $I_{DRV}$  は受信側の検出抵抗  $R_L \cdot I_{DRV}$  に変換され、差動増幅器が差動入力の A/D コンバータで処理される。

図 23: アナログ信号 定電流ソース → 抵抗負荷、絶縁増幅器入力

### 3.1.2 ポートの終端の影響

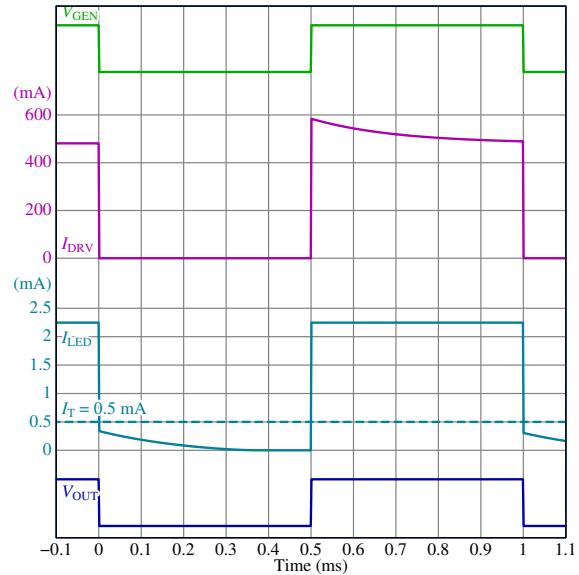

このラインを結合回路で AC 終端した時、図 22 のように結合回路の  $C_1$  と  $R_1$  ( $1 \mu\text{F}$  と  $200 \Omega$ ) を直列としたものが検出抵抗  $R_L$  と並列に接続されたような形となる。

だが、出力されるアナログ信号は典型的には一定の値となるか緩やかに変化するものとなりそうで、またこの種の電流源は容量性負荷の接続に耐えられそうであり、その場合は結合回路の接続は影響を与えないだろう。

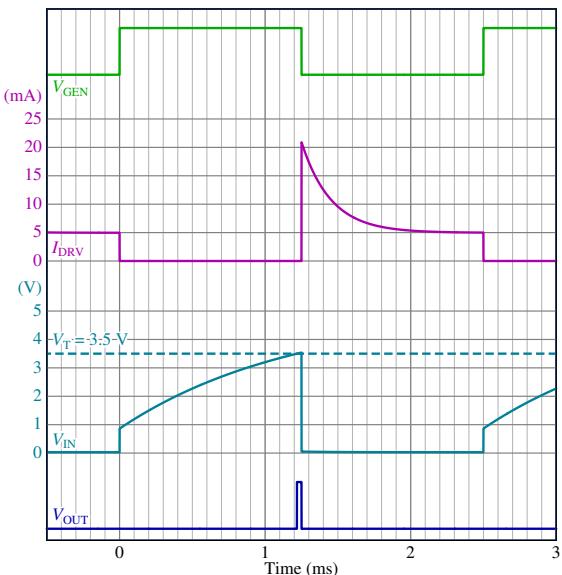

アナログ信号がステップ的に変化する場合には図 23 にイメージを示すように若干の応答の遅れが予期される。だが、このタイプのアナログ出力の性質上、通常はこの応答の遅れもさほど問題となりそうにない。

## 4 まとめ

結合回路による AC 終端 (図 1) は、DC 成分がその  $1 \mu\text{F}$  のコンデンサで阻止されることから、結合回路による DC 終端<sup>[2.1]</sup> の場合と比較すれば問題を起こしにくい。

だが、結合回路による AC 終端は相当の容量性負荷を与え、例えば上でいくつかの例を示したような信号の有意な遅れを、場合によっては信号の喪失を引き起こす可能性がある。

この可能性は上で例示したように事前に机上で分析するか予備試験を行なって確認し、必要に応じて適切な対応を行なうことが望ましい。

本稿ではいくつかの例について結合回路による AC 終端の影響に対する可能かも知れない対処方法

を示したが、それらは回路定数や回路そのものの変更を伴い、妨害に対する挙動を変える可能性があるため、それが試験の目的を損なわないかどうかは別途検討が必要となるであろう。

## 5 参考資料

- [1] IEC 61000-4-16:2015, *Electromagnetic compatibility (EMC) — Part 4-16: Testing and measurement techniques — Test for immunity to conducted, common mode disturbances in the frequency range 0 Hz to 150 kHz*

- [2] IEC 61000-4-16 の概要 — 低周波伝導コモンモード妨害イミュニティ試験の方法、株式会社 e・オータマ 佐藤, 2024-2025,

<https://www.emc-ohtama.jp/emc/reference.html>

- [2.1] IEC 61000-4-16 の概要 — 追補 1: DC 電圧試験における結合回路による終端の影響