# IEC 61000-4-16 の概要 — 追補 1: DC 電圧試験における結合回路による終端の影響

株式会社 e・オータマ 佐藤智典

2025 年 11 月 18 日

## 目 次

|          |                                    |    |

|----------|------------------------------------|----|

| <b>1</b> | <b>概要</b>                          |    |

| <b>2</b> | <b>デジタル I/O ポート、デジタル通信ポート</b>      |    |

| 2.1      | 非絶縁 NPN オープン・コレクタ出力 → 抵抗プルアップ、電圧入力 | 1  |

| 2.1.1    | 通常の動作                              | 2  |

| 2.1.2    | ポートの終端に伴う問題                        | 2  |

| 2.1.3    | この問題の回避                            | 3  |

| 2.2      | 非絶縁 NPN オープン・コレクタ出力 → リレー負荷        | 3  |

| 2.2.1    | 通常の動作                              | 3  |

| 2.2.2    | ポートの終端に伴う問題                        | 3  |

| 2.2.3    | この問題の回避                            | 4  |

| 2.3      | 非絶縁 NPN オープン・コレクタ出力 → フォトカプラ絶縁入力   | 4  |

| 2.3.1    | 通常の動作                              | 4  |

| 2.3.2    | ポートの終端に伴う問題                        | 4  |

| 2.3.3    | この問題の回避                            | 4  |

| 2.4      | フォトカプラ絶縁入力 ← 非絶縁 NPN オープン・コレクタ出力   | 5  |

| 2.4.1    | 通常の動作                              | 5  |

| 2.4.2    | ポートの終端に伴う問題                        | 5  |

| 2.5      | 非絶縁 PNP オープン・コレクタ出力 → フォトカプラ絶縁入力   | 5  |

| 2.5.1    | 通常の動作                              | 5  |

| 2.5.2    | ポートの終端に伴う問題                        | 5  |

| 2.6      | フォトカプラ絶縁出力 → 抵抗プルアップ、電圧入力          | 6  |

| 2.6.1    | 通常の動作                              | 6  |

| 2.6.2    | ポートの終端に伴う問題                        | 6  |

| 2.6.3    | この問題の回避                            | 6  |

| 2.7      | TIA/EIA/RS 422, 485                | 6  |

| 2.7.1    | ポートの終端に伴う問題                        | 7  |

| 2.8      | Ethernet                           | 7  |

| 2.8.1    | ポートの終端に伴う問題                        | 7  |

| <b>3</b> | <b>アナログ I/O ポート</b>                |    |

| 3.1      | アナログ信号 定電流ソース → 抵抗負荷、絶縁増幅器入力       | 7  |

| 3.1.1    | 通常の動作                              | 7  |

| 3.1.2    | ポートの終端に伴う問題                        | 7  |

| 3.1.3    | この問題の回避                            | 8  |

| 3.2      | アナログ信号 定電流シンク → 抵抗負荷、絶縁増幅器入力       | 8  |

| 3.2.1    | 通常の動作                              | 8  |

| 3.2.2    | ポートの終端に伴う問題                        | 8  |

| 3.2.3    | この問題の回避                            | 9  |

| 3.3      | 抵抗負荷、非絶縁増幅器入力 ← アナログ信号 定電流ソース      | 9  |

| 3.3.1    | 通常の動作                              | 9  |

| 3.3.2    | ポートの終端に伴う問題                        | 9  |

| 3.3.3    | この問題の回避                            | 9  |

| 3.4      | 4 線式測温抵抗体入力 ← Pt100 測温抵抗体          | 10 |

| 3.4.1    | 通常の動作                              | 10 |

| 3.4.2    | ポートの終端に伴う問題                        | 10 |

| 3.4.3    | この問題の回避                            | 10 |

| <b>4</b> | <b>まとめ</b>                         | 10 |

| 4.1      | デジタル I/O ポート                       | 10 |

| 4.2      | アナログ I/O ポート                       | 11 |

| <b>5</b> | <b>参考資料</b>                        | 11 |

## 1 概要

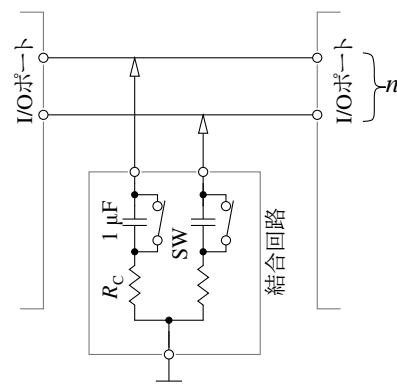

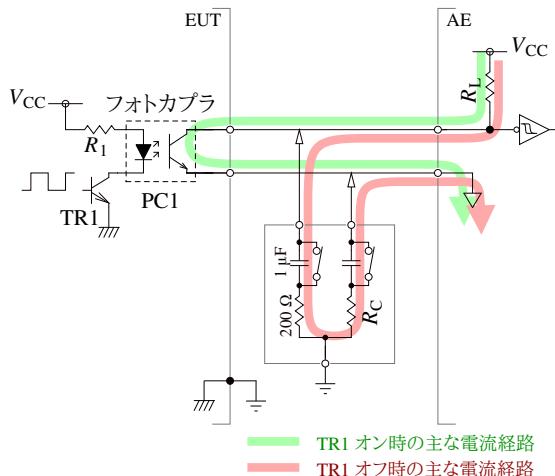

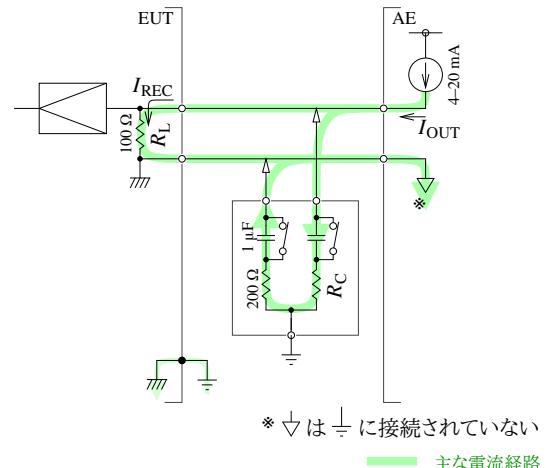

IEC 61000-4-16<sup>[1][2]</sup> の試験に際して、妨害の注入の対象となる非シールド線の接続が意図されたポートはそのポートに妨害を注入する時以外は図 1 のように結合回路を介して接地することで終端<sup>[1]</sup>することになるだろう。

だが、これがポートの動作に無視できない影響を与え、試験の適切な実施を妨げることがある。

$$R_C = n \times 100 \Omega$$

SW: DC 電圧試験では閉じる

図 1: 妨害が印加されていないポートの終端の例

特に DC 電圧試験 (DC の妨害を注入する試験) では妨害の注入に用いる結合回路のみでなくそれらの

<sup>[1]</sup> そのポートの AE (対向器) 側は何らかの手段によって他からアイソレートされ、この結合回路は EUT から見たコモン・モード・インピーダンスを 100 Ω とすることから、規格ではその用語は用いられていないが本稿では“終端”と呼ぶ。

結合回路全ての SW も閉じて  $1 \mu\text{F}$  のコンデンサを短絡する(以降、“DC 終端”と呼ぶ)ことが、すなわち実質的にそれらのポートの各ラインを抵抗を介して接地に直接接続することが必要となり、ポートの動作に影響を与える可能性が特に高くなる。

本稿では IEC 61000-4-16 のこの DC 電圧試験における“DC 終端”によって生じることがある問題の例について、またその一部については可能かも知れない対処方法<sup>†2†3</sup>について述べる。

そのポートに妨害を注入する際には例えば DC  $\pm 10 \text{ V}$  や DC  $\pm 100 \text{ V}$  の妨害電圧が  $50 \Omega$  の抵抗を介して結合回路に注入され、そのポートの各端子に高い電圧や電流を生じさせることが予期される<sup>†4</sup>が、これは本稿では扱わない。

また、AC 電圧試験に際しては結合回路の SW を開いて抵抗と直列に  $1 \mu\text{F}$  のコンデンサが入った形とするが、これも本稿では扱わない。

## 2 デジタル I/O ポート、デジタル通信ポート

### 2.1 非絶縁 NPN オープン・コレクタ出力 → 抵抗プルアップ、電圧入力

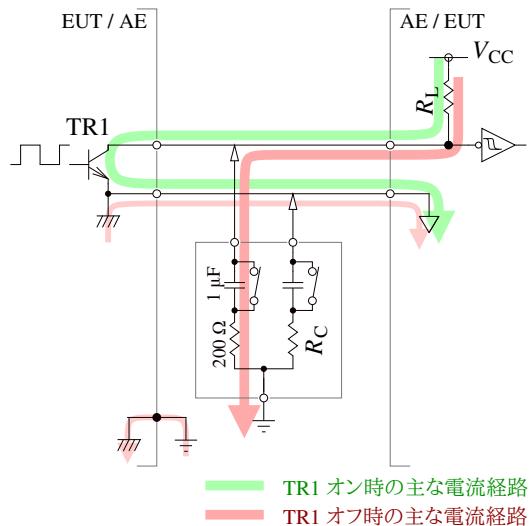

ここでは、図 2<sup>†5</sup>に示すような、オープン・コレクタの出力を抵抗 ( $R_L$ ) でプルアップして論理信号として受け取る単純な非絶縁インターフェースについて考える。

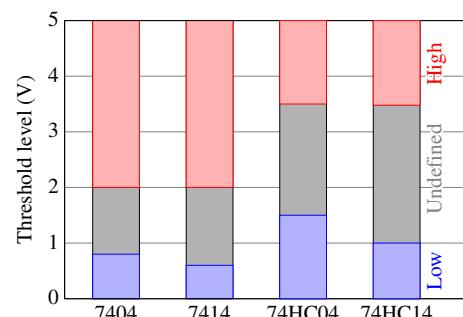

受信レベルの閾値はレシーバに依存し、レシーバとして標準ロジックを用いるとしてもファミリや電源電圧による相違が、またファミリ内でも若干の相違があるが、ここでは図 3 に 74HC14 として示したようなものを想定する。

図 2: 非絶縁 NPN オープン・コレクタ出力 → 抵抗プルアップ、電圧入力

図 3: ロジック入力の閾値の例 ( $V_{CC} = 5 \text{ V}$ )

#### 2.1.1 通常の動作

結合回路を接続していない通常の動作状態では、TR1 がオン(導通)の時は受信端の電圧は  $0 \text{ V}$  近くまで引き下げられてロー・レベルとなり、TR1 がオフ(非導通)の時は受信端の電圧はプルアップ抵抗  $R_L$  によって受信側の  $V_{CC}$  近くまで引き上げられられてハイ・レベルとなる。

#### 2.1.2 ポートの終端に伴う問題

これらのラインを結合回路で DC 終端すると、この回路の動作は大きな影響を受ける。

TR1 がオンの時に受信端の電圧が  $0 \text{ V}$  近くまで引き下げられてロー・レベルとなることには変わりない。

だが、TR1 がオフの時は、結合回路の抵抗  $R_C$  ( $= 200 \Omega$ ) が受信側のプルアップに拮抗して入力電圧を引き下げる形となり、入力電圧は有意に低くな

<sup>†2</sup> ここで示す対処方法は回路定数や回路そのものの変更を伴い、それが試験対象のシステムの動作や試験に悪影響を与えるいかどうかは別途検討が必要となるであろう。

<sup>†3</sup> 回路定数や回路そのものの変更を行なった EUT を試験などで試験する場合、その変更の情報はテスト・プランに含めるか、あるいは試験後に速やかにテスト・プランの追補として提出することが望ましいだろう。

<sup>†4</sup> 本稿で示した回路のいくつかはそのような妨害に耐えられないことが予期される。長距離での接続には耐性の高い回路の使用を、及び/もしくはシールドの適切な適用を考慮することを推奨する。

<sup>†5</sup> ここでは実際には存在するかも知れないフィルタや保護回路は示していない。以下も同様。

る。例えばプルアップ抵抗  $R_L = 1 \text{ k}\Omega$ 、受信側の電源電圧  $V_{CC} = 5 \text{ V}$  として考えると、TR1 がオフの時の入力電圧は電源電圧  $V_{CC}$  をプルアップ抵抗  $R_L = 1 \text{ k}\Omega$  と結合回路の抵抗  $R_C = 200 \Omega$  で分圧したものとなることから  $V_{CC} \cdot R_C / (R_C + R_L) \approx 0.8 \text{ V}$  程度までしか上がらないようになる。このため、レシーバの閾値が 図 3 で 74HC14 として示したようなものと仮定すると、送信側の状態に関わらず受信レベルはロー・レベルのままとなることが予期される。

EUT を接地し、AE を接地せずに試験するとしても、図 2 のような構成では EUT と AE の 0 V が相互接続されることから EUT と AE を逆にしても挙動は同様となるであろう。

### 2.1.3 この問題の回避

駆動能力に余裕がある場合、プルアップ抵抗  $R_L$  を小さくすることでこの問題を回避できる可能性がある。

例えば  $V_{CC} = 5 \text{ V}$  の場合、TR1 がオンとなった時に 0.1 A を流せるならば、プルアップ抵抗  $R_L$  を  $50 \Omega$  とすれば TR1 がオフとなった時の受信端の電圧を 4 V まで上げて受信レベルをハイ・レベルとできるであろう。

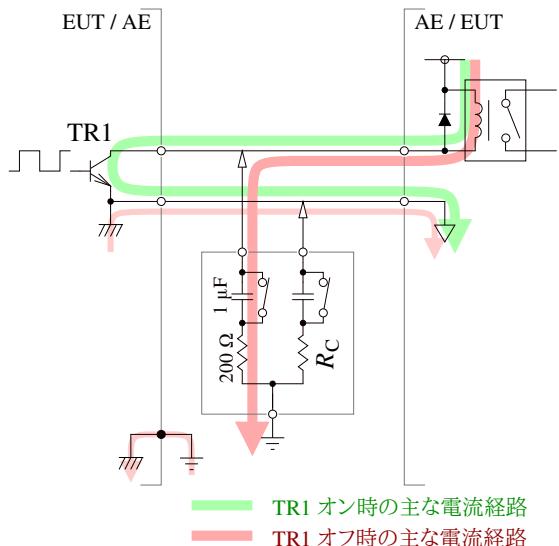

## 2.2 非絶縁 NPN オープン・コレクタ出力 → リレー負荷

先の例と似ているが、ここでは図 4 のように非絶縁オープン・コレクタの出力でリレーを直接駆動する場合について考える。

### 2.2.1 通常の動作

リレーは、動作電圧は定格電圧の  $x\%$  以下（例えば 80 % 以下）、復帰電圧は定格電圧の  $y\%$  以上（例えば 15 % 以上）のように規定された特性を持ち、リレーを確実に動作させるためには動作電圧以上の電圧を印加し、確実に復帰させる（コイルに通電していなかった時の状態に戻す）ためには印加電圧を復帰電圧以下まで下げることが求められる。これは動作電圧よりも低ければ動作しないことを、あるいは復帰電圧よりも高ければ復帰しないことを意味するわけではないので、意図せずに動作させない

図 4: 非絶縁 NPN オープン・コレクタ出力 → リレー負荷

ためには復帰電圧以下の電圧を、また意図せずに復帰させないためには動作電圧以上の電圧を保つことが必要となるだろう。

結合回路を接続していない通常の動作状態では、TR1 がオフの時はコイルに印加される電圧はほぼゼロとなってリレーは動作せず、TR1 がオンとなるとコイルに電源電圧（ここではリレーの定格電圧と等しいと仮定）に近い電圧が印加されてリレーは動作する。

### 2.2.2 ポートの終端に伴う問題

このラインを結合回路で DC 終端した時、TR1 がオフの時も結合回路の抵抗  $R_C (= 200 \Omega)$  を介してリレーのコイルに通電することから、TR1 の状態と無関係にリレーが動作しないままとなる、あるいはリレーが一度動作するとその後で TR1 がオフとなっても復帰しない可能性が予期される。

例えばリレーの動作電圧が 80 % 以下、復帰電圧が 15 % 以上で、定格 24 V や 48 V の小型リレーでそうなるかも知れないようにコイル抵抗が  $1 \text{ k}\Omega$  程度以上の場合、図 4 のように結合回路での DC 終端を行なうと TR1 がオフの時もリレーに印加される電圧は結合回路の  $R_C$  の影響で動作電圧を超え、TR1 の状態と無関係に（本来は動作しないことが期待される場合にも）リレーは確実に動作することになる。

リレーのコイル抵抗が  $300\ \Omega$  程度としても TR1 がオフの時に電源電圧の 60 % 程度の電圧がリレーに印加された状態となり、これでもリレーが意図せずに動作するかも知れず、あるいは一度 TR1 がオンとなってリレーが動作した後に TR1 がオフとなつた時にリレーが復帰しないままとなるかも知れない。

### 2.2.3 この問題の回避

駆動能力に余裕があり、またそれを許容できるならば、リレーのコイルと並列に抵抗を接続して TR1 がオフの時に印加される電圧が復帰電圧を下回るようにしてこの問題を回避できるかも知れない。

例えばリレーの復帰電圧が 15 % 以上とすると、リレーのコイルと並列に  $35\ \Omega$  以下の抵抗を並列に接続すればコイル抵抗と無関係に TR1 がオフの時に印加される電圧は復帰電圧を下回るようになる。

但し、このような抵抗の追加は電流や電力をかなり増加させる可能性があり、例えば電源電圧が  $48\ V$  の場合は電流を  $1.4\ A$ 、また必要な電力を各チャネルについて  $66\ W$  程度増やす計算となる。従って、この方法を用いようとする場合は駆動能力を良く確認することが、そして必要であれば増強することが必要となりそうである。

## 2.3 非絶縁 NPN オープン・コレクタ出力 → フォトカプラ絶縁入力

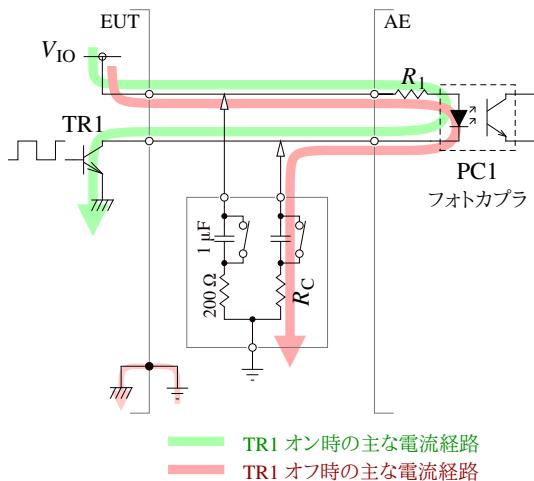

ここでは図 5 のように EUT 側からの単純な非絶縁オープン・コレクタの出力を AE 側のフォトカプラで受ける場合について考える。

これは先の §2.1 や §2.2 の例と似ているが、負荷の違いに加えて、出力側 (EUT 側) から供給される I/O 電源 ( $V_{IO}$ ) を利用することで受信側 (AE 側) を絶縁されたままとすることも想定している。

### 2.3.1 通常の動作

結合回路を接続していない通常の動作状態では、TR1 がオフの時はフォトカプラの LED には電流は流れずにフォトカプラの出力はオフ状態となり、TR1 がオンとなると LED に通電してフォトカプラの出力はオン状態となる。

図 5: 非絶縁 NPN オープン・コレクタ出力 (EUT 側) → フォトカプラ絶縁入力 (AE 側)

### 2.3.2 ポートの終端に伴う問題

このラインを結合回路で DC 終端した時、TR1 がオフの時も結合回路の抵抗  $R_C$  ( $= 200\ \Omega$ ) を介してフォトカプラの LED に通電することから、TR1 の状態と無関係にフォトカプラの出力がオン状態となることが予期される。

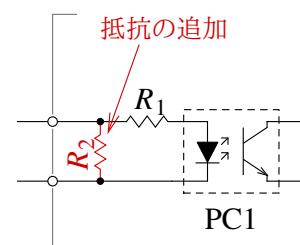

### 2.3.3 この問題の回避

それを許容できる場合、図 6 に示すように受信端に並列に抵抗を追加して TR1 がオフの時に受信端に加わる電圧を下げることによってこの問題を回避できるかも知れない。

例えば  $V_{IO} = 5\ V$  の場合、この抵抗  $R_2$  を  $50\ \Omega$  とすると TR1 がオフの時に受信端に加わる電圧は約  $1\ V$  となり、フォトカプラの LED に流れる電流は著しく小さくなるであろう。

但し、これは TR1 がオンの時の出力電流を増大させること、例えば  $V_{IO} = 5\ V$ 、 $R_2 = 50\ \Omega$  の場合でも出力電流を  $0.1\ A$  増大させることに注意が必要かも知れない。

図 6: §2.3.2 の問題への対処の例

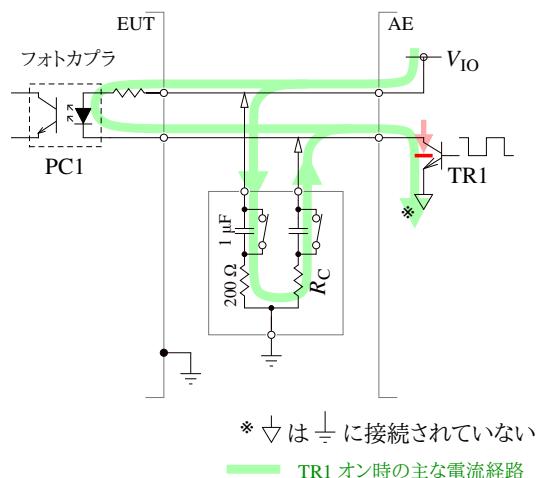

## 2.4 フォトカプラ絶縁入力 ← 非絶縁 NPN オープン・コレクタ出力

ここでは §2.3 と似ているが EUT と AE が逆の、すなわち図 7 のように AE 側からの単純な非絶縁オープン・コレクタの出力を EUT 側のフォトカプラで受ける場合について考える。

これらは同じように思えるかも知れないが、この試験では、EUT は接地し、AE 側は減結合する（実際上、絶縁する）ことから大きな違いを生じることが予期される。

図 7: フォトカプラ絶縁入力 (EUT 側) ← NPN オープン・コレクタ出力 (AE 側)

### 2.4.1 通常の動作

§2.3.1 と同様、結合回路を接続していない通常の動作状態では、TR1 がオフの時はフォトカプラの LED には電流は流れずにフォトカプラの出力はオフ状態となり、TR1 がオンとなると LED に通電してフォトカプラの出力はオン状態となる。

### 2.4.2 ポートの終端に伴う問題

この構成では §2.3.2 の場合と異なり結合回路で DC 終端を行なってもそれを通してグランドに電流が抜けることはなく、従って TR1 がオフとなった時にはフォトカプラの LED への電流は意図されたように遮断される筈である。

一方、TR1 がオンとなった時には受信端と並列に  $R_C \times 2 (= 400 \Omega)$  が接続された形となるが、これは若干の追加の負荷を与えるだけであろう。

このため、この構成においては結合回路による DC 終端は顕著な問題は引き起こしそうない。

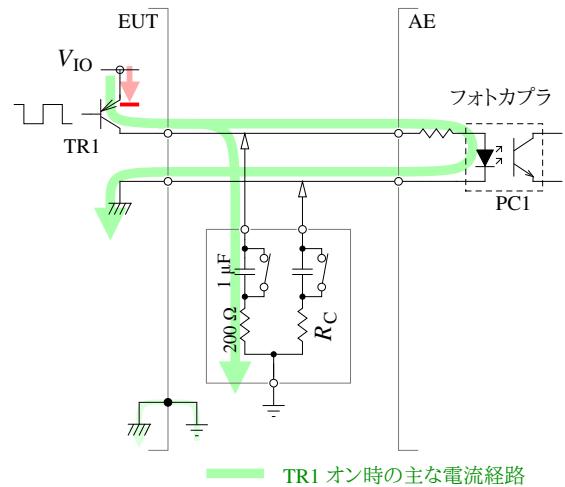

## 2.5 非絶縁 PNP オープン・コレクタ出力 → フォトカプラ絶縁入力

ここでは、§2.3 と同様に受信側 (AE 側) でフォトカプラを用いるが、出力側 (EUT 側) を図 8 のように非絶縁の PNP オープン・コレクタ出力でソースする形とした場合を考える。

図 8: PNP オープン・コレクタ出力 → フォトカプラ絶縁入力

### 2.5.1 通常の動作

NPN と PNP の相違はあるが §2.3.1 と同様、結合回路を接続していない通常の動作状態では、TR1 がオフの時はフォトカプラの LED には電流は流れずにフォトカプラの出力はオフ状態となり、TR1 がオンとなると LED に通電してフォトカプラの出力はオン状態となる。

### 2.5.2 ポートの終端に伴う問題

このラインを結合回路で DC 終端した時、單に、TR1 がオンの時はフォトカプラと結合回路の抵抗の双方に電流が流れ、TR1 がオフの時はこの電流は遮断されるようになる。

このため、TR1 がオンの時の出力電流はあるものの、この構成においては結合回路による DC 終端は顕著な問題は引き起こしそうない。

## 2.6 フォトカプラ絶縁出力 → 抵抗プルアップ、電圧入力

ここでは、図9のように、EUT側(送信側)からの出力がフォトカプラで絶縁されており、それをAE側(受信側)で抵抗でプルアップして論理信号として受け取る場合を考える。

図9: フォトカプラ絶縁出力 → 抵抗プルアップ、電圧入力

§2.4の場合と同様、この構成でもEUT側とAE側の双方が絶縁された状態となると想定される。

### 2.6.1 通常の動作

結合回路を接続していない通常の動作状態では、フォトカプラPC1がオンの時は受信端の電圧は0V近くまで引き下げられてロー・レベルとなり、PC1がオフの時は受信端の電圧はプルアップ抵抗 $R_L$ によって受信側の $V_{CC}$ 近くまで引き上げられられてハイ・レベルとなる。

### 2.6.2 ポートの終端に伴う問題

このラインを結合回路でDC終端した時、PC1がオンの時に受信端の電圧が0V近くまで引き下げられてロー・レベルとなることには変わりない。

だが、PC1がオフの時は、そのラインを結合回路でDC終端してもグランドに電流が抜けることはないものの、結合回路の抵抗 $R_C$ 2つ( $=200\Omega$ )を通してライン間が接続されて入力電圧を引き下げる形となる。

例えばプルアップ抵抗 $R_L=1k\Omega$ 、受信側の電源電圧 $V_{CC}=5V$ とすると、フォトカプラの出力がオ

フの時も受信端の電圧は $V_{CC} \cdot 2R_C/(2R_C + R_L) \simeq 1.4V$ 程度までしか上がりず、受信レベルはハイ・レベルとならない。

### 2.6.3 この問題の回避

条件によっては、プルアップ抵抗 $R_L$ を小さくしてフォトカプラの出力がオフとなった時の入力電圧がレシーバのハイ・レベルの閾値を超えるようにすることでこの問題を回避できる可能性がある。

例えば閾値が図3で74HC14として示したものとしても $R_L \leq 150\Omega$ とすれば入力電圧が3.6Vを超えて、また閾値が7414として示したものとすれば $R_L \leq 600\Omega$ とすれば入力電圧が2Vを超えてその状態での受信レベルはハイ・レベルとなるであろう。

但し、フォトカプラの出力がオンとなった時の受信レベルをロー・レベルとするため、フォトカプラが $R_L = 150\Omega$ とした場合は30mA程度、 $R_L = 600\Omega$ とした場合は8mA程度の電流を流して受信レベルをロー・レベルとできることも必要となる。

フォトカプラの最大コレクタ電流が所望の電流以上であるがEUT上のフォトカプラがその電流を出力できない場合、フォトカプラをオンさせる際にLEDに流す電流を増やすことで対応できるかも知れない。これは図9では $R_1$ を小さくすることで行なえるが、このためにはフォトカプラを駆動するドライバ(図9ではTR1として示した)が所望の電流を出力可能であることも必要となる。

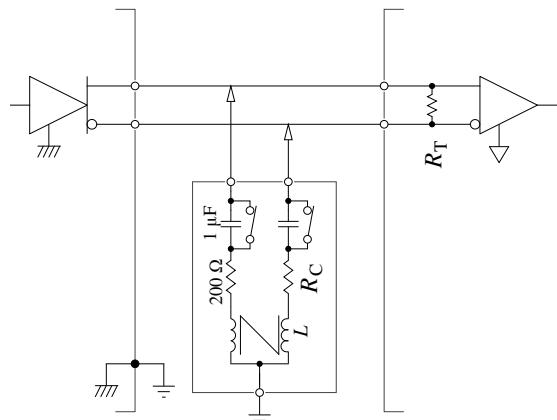

## 2.7 TIA/EIA/RS 422, 485

TIA/EIA/RS 422(以降、RS 422)やTIA/EIA/RS 485(以降、RS 485)は平衡伝送方式によるもので、1km程度までの距離の通信に用いられる。10Mbpsまでの通信速度をカバーするが、1kmでは100kbps程度、100mでは1Mbps程度のように通信速度は距離とのトレードオフとなり、長距離においては比較的低速の通信での使用が想定される。

RS 422は $1:n$ (1台のドライバと複数台のレシーバ)の接続となるのに対し、RS 485は $n:n$ ( $n \leq 32$ )のマルチ・ドロップ接続を行なうことができる。

図 10: TIA/EIA/RS 422

### 2.7.1 ポートの終端に伴う問題

この通信ラインは良好な平衡を持ち、従つて図10のようなその通信ラインの結合回路によるDC終端はコモン・モードでの影響を与えることになる。

この通信ラインは 100 Ω 程度で (RS 485 の場合はバスの両端で 100 Ω 程度で) 終端され、またトランシーバはある程度のコモン・モード妨害への耐性を考慮して設計されており、この通信ラインの結合回路での DC 終端はその動作に有意な悪影響を与えないことが期待されそうである。

## 2.8 Ethernet

ツイスト・ペア Ethernet は高速通信のための通信方式の 1 つで、UTP (unshielded twisted pair) ケーブル、もしくは STP (shielded twisted pair) ケーブルを用いて 1 対 1 の接続を行なうことができる。

### 2.8.1 ポートの終端に伴う問題

この試験の対象となるような状況ではツイスト・ペア Ethernet の接続には STP ケーブルが用いられることが多いように見受けられ、その場合、本稿で述べるような問題の懸念はない。

UTP ケーブルの使用が想定されるとしても、Ethernet ポートはパルス・トランスによってアイソレートされている筈で、そのポートに適した結合回路があるならばそれを通して DC 終端を行なってもポートの動作に影響を与えそうになく、またそのポートの DC 終端の有無は DC 電圧試験の結果に全く影響しそうにない。

## 3 アナログ I/O ポート

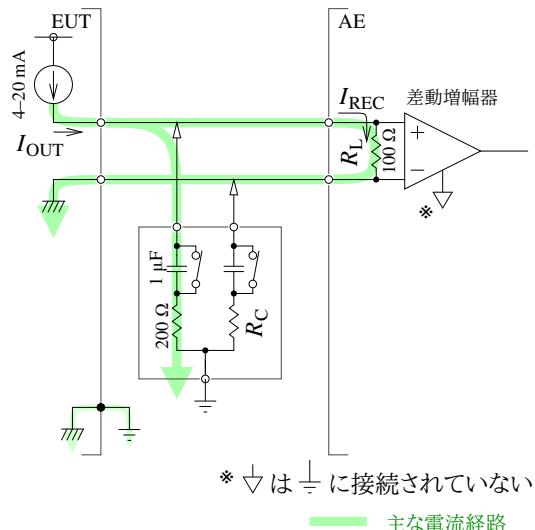

### 3.1 アナログ信号 定電流ソース → 抵抗負荷、絶縁増幅器入力

ここでは 図11 のような EUT 側から定電流でソースされるアナログ信号電流  $I_{OUT}$  を AE 側で検出抵抗  $R_L$  で受けている場合について考える。

図 11: アナログ信号 定電流ソース → 抵抗負荷、絶縁増幅器入力

ソース側 (EUT 側) は絶縁されておらず、受信側 (AE 側) は絶縁増幅器かその他の何らかの手段でグランドや他の使用されるポートから絶縁された状態とされるものと想定している。

#### 3.1.1 通常の動作

出力側からソースされた電流  $I_{OUT}$  は受信側の検出抵抗  $R_L$  で電圧  $R_L \cdot I_{OUT}$  に変換され、差動増幅器が差動入力の A/D コンバータで処理される。

#### 3.1.2 ポートの終端に伴う問題

このラインを結合回路で DC 終端した時、検出抵抗  $R_L$  と並列に結合回路の抵抗  $R_C$  が接続される形となる。このため、信号電流  $I_{OUT}$  を出力した時の受信値  $I_{REC}$  は、 $\parallel$  を  $a \parallel b = ab/(a + b)$  なる二項演算子として、

$$I_{REC} = I_{OUT} \frac{R_L \parallel R_C}{R_L}$$

となる。

例えば  $R_L = 100 \Omega$  とした場合、 $R_C = 200 \Omega$  であるので、 $I_{REC} \simeq 0.67 I_{OUT}$  に、例えば出力値  $I_{OUT}$  が 10 mA の時の受信値  $I_{REC}$  は約 6.7 mA という計算となる。

### 3.1.3 この問題の回避

この問題には例えば次のような方法で対応できるかも知れない:

- 検出抵抗  $R_L$  を  $R_L = R'_L \parallel R_C$  となる  $R'_L$  に、すなわち  $R'_L = R_C R_L / (R_C - R_L)$  に変更する。

例えば上の例では、 $R_L = 100 \Omega$ 、 $R_C = 200 \Omega$  として、 $R'_L = 200 \Omega$  となる。

- 受信値の基準値を結合回路による DC 終端の影響を考慮した値に、上の例では出力値の 0.67 倍に変更する。

- その逆に、出力値  $I_{OUT}$  を結合回路による DC 終端の影響を考慮して受信値が意図された値となる値に、上の例では意図された値の  $1/0.67$  倍に変更する。

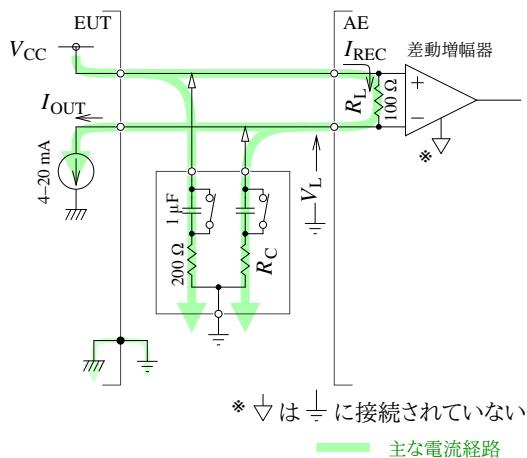

## 3.2 アナログ信号 定電流シンク → 抵抗負荷、絶縁増幅器入力

§3.1では定電流のソースを行なう場合について述べたが、ここでは逆に図 12 のような EUT 側から定電流でシンクされるアナログ信号電流  $I_{OUT}$  を AE 側で検出抵抗  $R_L$  で受けている場合について考える。

図 12: アナログ信号 定電流シンク → 抵抗負荷、絶縁増幅器入力

§3.1 の場合と同様に、シンク側 (EUT 側) は絶縁されておらず、受信側 (AE 側) は絶縁増幅器かその他の何らかの手段でグランドや他の使用されるポートから絶縁された状態とされるものと想定している。

### 3.2.1 通常の動作

出力側でシンクされた電流  $I_{OUT}$  は受信側の検出抵抗  $R_L$  で電圧  $R_L \cdot I_{OUT}$  に変換され、差動増幅器か差動入力の A/D コンバータで処理される。

### 3.2.2 ポートの終端に伴う問題

図 12のように定電流でシンクされるアナログ信号を抵抗で受けている場合、そのラインを結合回路で DC 終端すると検出抵抗  $R_L$  にはその電流に加えて終端回路の抵抗  $R_C$  を流れる電流が流れることになる。

アナログ信号がソースされている §3.1の場合と異なり、この影響はやや複雑な、レール電圧と出力電流に依存したものとなる。

レール電圧を  $V_{CC}$ 、出力値を  $I_{OUT}$ 、検出抵抗を  $R_L$ 、結合回路の抵抗を  $R_C$ 、シンクされている側のラインの電位を  $V_L$  とすると、 $R_L$  には  $I_{OUT}$  に加えて  $V_L/R_C$  の電流が流れるので、

$$V_L = V_{CC} - R_L \left( I_{OUT} + \frac{V_L}{R_C} \right)$$

より

$$V_L = \frac{R_C V_{CC} - I_{OUT} R_L R_C}{R_L + R_C}$$

受信値  $I_{REC}$  は、

$$I_{REC} = \frac{V_{CC} - V_L}{R_L} = \frac{V_{CC} + I_{OUT} R_C}{R_L + R_C}$$

となる。

例えば  $V_{CC} = 5 \text{ V}$ 、 $R_L = 100 \Omega$  とした場合、 $R_C = 200 \Omega$  であるので、

$$I_{REC} = \frac{5 + 200 I_{OUT}}{100 + 200} \simeq 16.7 \text{ (mA)} + 0.67 I_{OUT}$$

となり、 $I_{OUT} = 10 \text{ mA}$  の場合は  $I_{REC} \simeq 23 \text{ mA}$ 、 $I_{OUT} = 4 \text{ mA}$  の場合は  $I_{REC} \simeq 19 \text{ mA}$  となる。

### 3.2.3 この問題の回避

出力値  $I_{OUT}$  が固定の場合、この問題には例えば次のような方法で対応できるかも知れない:

- 検出抵抗  $R_L$  をその両端に発生する電圧が意図された値となるような値に変更する。

この抵抗値  $R'_L$  は次のように計算で求めることもできる:

$$R'_L = \frac{I_{OUT} R_C R_L}{V_{CC} + I_{OUT}(R_C - R_L)}$$

だが、検出抵抗  $R_L$  としてトリマを接続して所望の値を得られるように調整する方が簡単で、実際的かも知れない。

- 受信値の基準値を上で述べたような結合回路による DC 終端の影響を考慮した値に変更する。

だが、検出抵抗の両端に現れる電圧が受信側で扱える範囲を超えるかも知れず、その場合はこの方法では対応できない。

- その逆に、出力値  $I_{OUT}$  を結合回路による DC 終端の影響を考慮して受信値が意図された値となる値に変更する。

だが、出力値を可能な範囲で調整しても受信値を意図された値とすることはできないかも知れず、その場合はこの方法では対応できない。

## 3.3 抵抗負荷、非絶縁増幅器入力 ← アナログ信号 定電流ソース

図 13 のように、AE 側からソースされ、EUT 側で抵抗で受ける場合の挙動は §3.1 と幾分似たものとなる。

ここでは、図 13 のように、受信側 (EUT 側) は接地され、ソース側 (AE 側) は何らかの手段でグランドや他の使用されるポートから絶縁された状態とされることを想定している。

### 3.3.1 通常の動作

通常の動作は §3.1 と同様で、出力側でソースされた電流  $I_{OUT}$  は受信側の検出抵抗  $R_L$  で電圧  $R_L \cdot I_{OUT}$  に変換され、増幅器か A/D コンバータで処理される。

図 13: 抵抗負荷、非絶縁増幅器入力 ← アナログ信号 定電流ソース

### 3.3.2 ポートの終端に伴う問題

このケースではソース側 (AE 側) がフローティングとなっていることから結合回路で DC 終端を行なってもそれを通してグランドに電流が抜けることはなく、負荷と並列に  $R_C \times 2 (= 400 \Omega)$  が接続される形となる。

このため、信号電流  $I_{OUT}$  を出力した時の受信値  $I_{REC}$  は、

$$I_{REC} = I_{OUT} \frac{R_L \parallel 2R_C}{R_L}$$

となり、例えば  $R_L = 100 \Omega$  とした場合、 $R_C = 200 \Omega$  であるので、 $I_{REC} = 0.8 I_{OUT}$  に、例えば出力値  $I_{OUT}$  が 10 mA の時の受信値  $I_{REC}$  は 8 mA という計算となる。

### 3.3.3 この問題の回避

§3.1.3 と同様、この問題には例えば次のような方法で対応できるかも知れない:

- 検出抵抗  $R_L$  を  $R_L = R'_L \parallel 2R_C$  となる  $R'_L$  に、すなわち  $R'_L = 2R_C R_L / (2R_C - R_L)$  に変更する。

例えば上の例では、 $R_L = 100 \Omega$ 、 $R_C = 200 \Omega$  として、 $R'_L = 133 \Omega$  となる。

- 受信値の基準値を結合回路による DC 終端の影響を考慮した値に、上の例では出力値の 0.8 倍に変更する。

- その逆に、出力値  $I_{OUT}$  を結合回路による DC 終端の影響を考慮して受信値が意図された値となる値に、上の例では意図された値の  $1/0.8$  倍に変更する。

### 3.4 4 線式測温抵抗体入力 ← Pt100 測温抵抗体

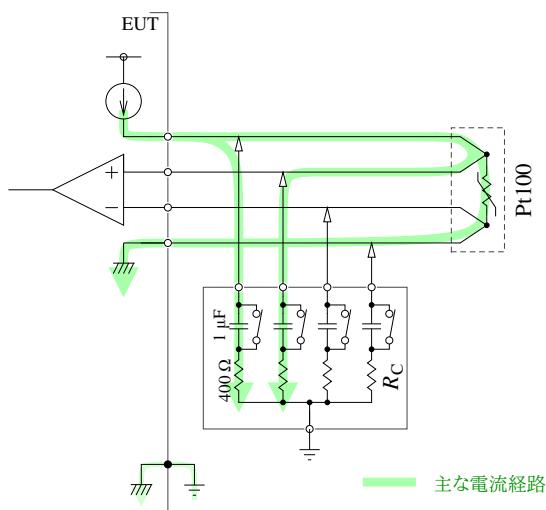

ここでは図 14 のように、測温抵抗体への励起電流を定電流でソースして検知された電圧を差動増幅器で測定する回路を考える。

実際の回路ではそのようにならないこともあるが、ここでは測温抵抗体の片側が  $0 \text{ V}$  に接続されるような測定回路を想定している。

図 14: 4 線式測温抵抗体入力 ← Pt100 測温抵抗体

#### 3.4.1 通常の動作

測温抵抗体 (Pt100) に電流を流してその両端に生じた電圧を差動増幅器で受けて処理する。

この電流と電圧からその測温抵抗体の抵抗値を求めることができ、その抵抗値からその測温抵抗体の温度を求めることができる。

#### 3.4.2 ポートの終端に伴う問題

このポートを図 14 のように結合回路で DC 終端すると Pt100 と並列に結合回路の抵抗  $R_C (= 400 \Omega)$  2つが接続された形となり、常温では合成抵抗が  $70 \Omega$  強となり  $-70^\circ\text{C}$  程度に、 $300^\circ\text{C}$  では  $100 \Omega$  強と

なり  $0^\circ\text{C}$  程度に相当する読みを与えるようになることが予期される。このため、その状態では意図したように試験を行なうことができないであろうだけでなく、それが加熱制御に用いられている場合にはそのまま動作させれば制御対象を過熱させ、場合によっては焼損させるかも知れない。

ここでは踏み込まないが、測温抵抗体の片側が  $0 \text{ V}$  に接続されていない場合にはかなり複雑な影響が予期される。

例えばしばしば測温抵抗体と  $0 \text{ V}$  とのあいだに電流検出抵抗が接続されるが、このような場合、上記のように結合回路の抵抗  $R_C$  が単純に測温抵抗体と並列に接続されるものと見ることができなくなるだけでなく、電流検出抵抗と並列に  $R_C$  が接続される形となることから測温抵抗体に流される電流を相当（だが駆動能力の限界から、おそらくは計算で求められる値ほどまでではなく）増加させることも予期される。

#### 3.4.3 この問題の回避

この問題には例えば次のような方法で対応できるかも知れない:

- 結合回路で DC 終端した状態で意図した読みを得られるように、励起電流を増やす;

- 結合回路で DC 終端した状態での読みに合わせて温度の基準値を調整する;

- 結合回路で DC 終端した状態で意図した読みを得られるように、Pt100 と直列に抵抗を接続する。

## 4 まとめ

### 4.1 デジタル I/O ポート

上の §2でいくつかの例を示したように、デジタル I/O ポートを結合回路で DC 終端した場合、送信側の出力の論理状態に関わらずいずれか一方の状態が出力されているかのように受信側や負荷を反応させる可能性がある。この可能性は上で例示したように事前に机上で分析するか予備試験を行なって確認し、必要に応じて適切な対応を行なうことが望ましい。

また、試験に際しては、望ましくは送信側で出力の論理状態を切り替えながら、さもなくば双方の論理状態として動作させ、かつ受信側や負荷がその出力に正しく応答していることを確認すべきである。

そのようにしていれば、本稿で述べるような問題が発生した場合は妨害を印加していない時でも不合格と判定される状態となってそれに気付かされることになるであろうし、そのような状態とならずに試験を行なえたならばそれが送信側と受信側のいずれに起因するものであれ伝達された論理状態のいずれの誤りも検知できるであろう。

そのような形で動作させていない場合、本稿で述べるような問題が発生していても気付かれないとなるかも知れないだけでなく、妨害の影響で入出力が誤動作した、例えば送信側が誤動作して出力が反転したとしてもその誤動作が検知されずに誤って合格と判定されることになるかも知れない。

本稿ではいくつかの例について結合回路によるDC終端の影響に対する可能かも知れない対処方法を示したが、それらは回路定数や回路そのものの変更を伴い、妨害に対する挙動を変える可能性があるため、それが試験の目的を損なわないかどうかは別途検討が必要となるであろう。

## 4.2 アナログ I/O ポート

上の §3でいくつかの例を示したように、アナログ I/O ポートの結合回路での DC 終端は受信値を有意に変動させる可能性が予期される。この可能性は上で例示したように事前に机上で分析するか予備試験を行なって確認し、必要に応じて適切な対応を行なうことが望ましい。

また、試験に際しては、送信側と受信側のいずれが EUT である場合でも受信値の監視を何らかの手段で行なうべきである。

そのようにしていれば、本稿で述べるような問題が発生した場合は妨害を印加していない時でも不合格と判定される状態となってそれに気付かされることになるであろうし、そのような状態とならずに試験を行なえた時には送信側と受信側のいずれに起因する値の変動も検知できるようになるであろう。

受信値があらかじめ設定された許容幅を超えないかどうかのみが確認されている場合もあるが、通常の許容幅では受信値の有意な変動があっても検知で

きないかも知ないので、その許容幅がこの試験の目的のために適切かどうかを確認し、必要に応じてその調整や別の手段での監視を考慮すべきかも知れない。また、受信値が片側の限界（上限、もしくは下限）を超えないかどうかのみを確認している<sup>†6</sup>場合、結合回路による DC 終端によってその逆の方向の変動が引き起こされたとしても気付かれないであろうし、その状態で試験を行なった場合は受信値に大きな変動があっても検知されずにそれが見落されるままとなるかも知ないので、他の適当な手段での監視も考慮すべきかも知れない。

## 5 参考資料

[1] IEC 61000-4-16:2015, *Electromagnetic compatibility (EMC) — Part 4-16: Testing and measurement techniques — Test for immunity to conducted, common mode disturbances in the frequency range 0 Hz to 150 kHz*

[2] IEC 61000-4-16 の概要 — 低周波伝導コモンモード妨害イミュニティ試験の方法、株式会社 e・オータマ 佐藤, 2024–2025,

<https://www.emc-ohtama.jp/emc/reference.html>